Hardware parameters

购买链接

Specification of parameters

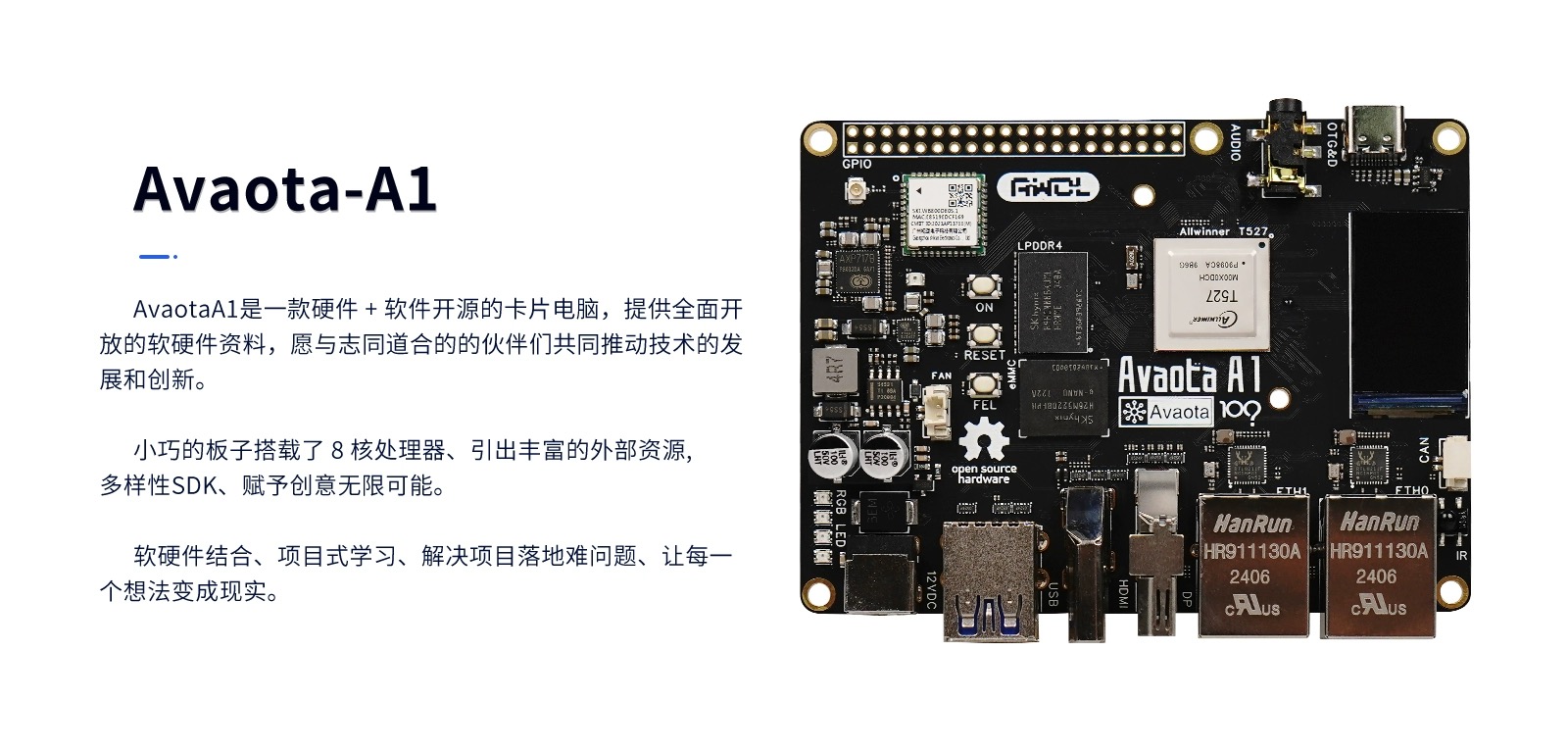

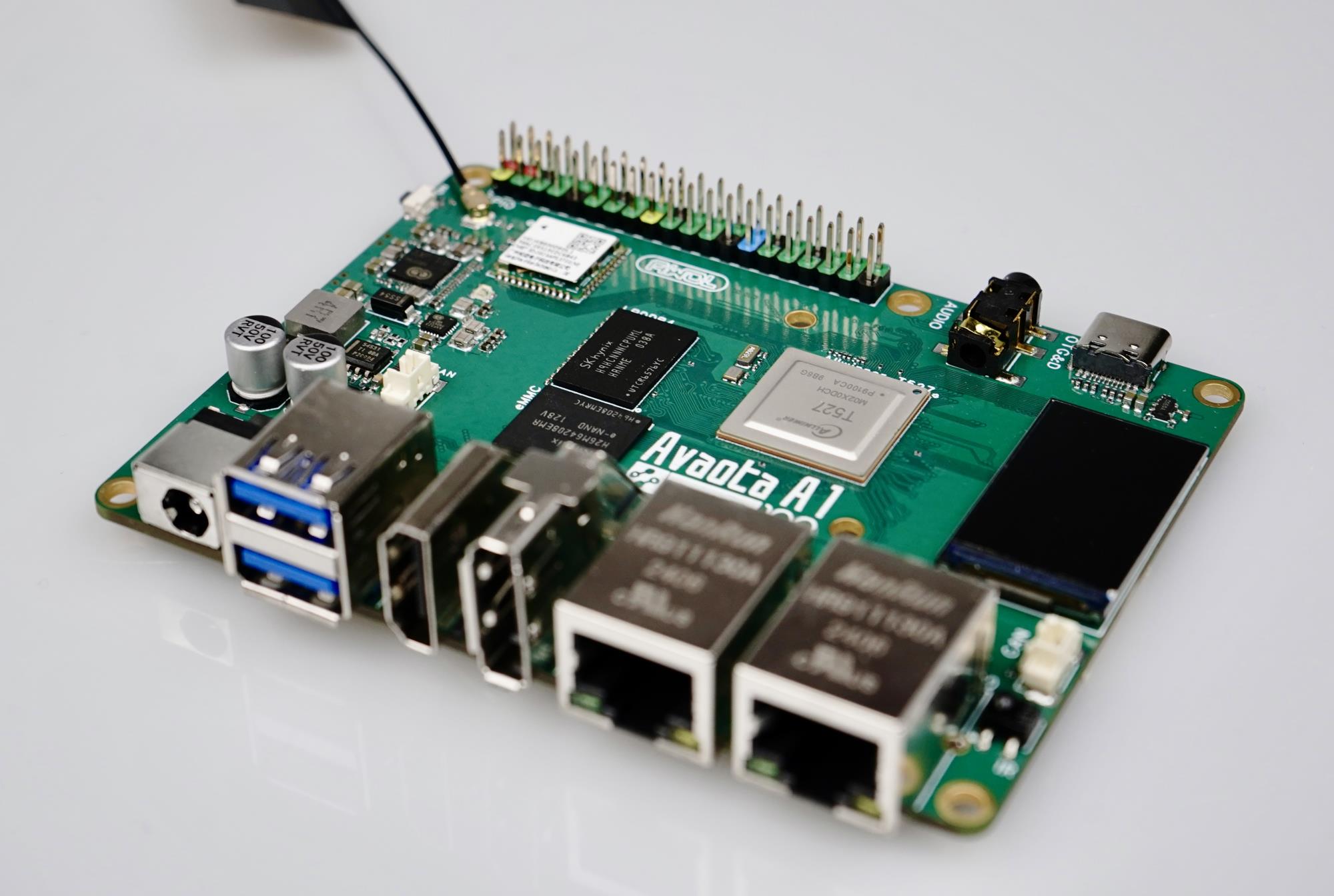

Avaota-A1 - A Powerful SBC with Allwinner T527 Octa-Core A55 SoC

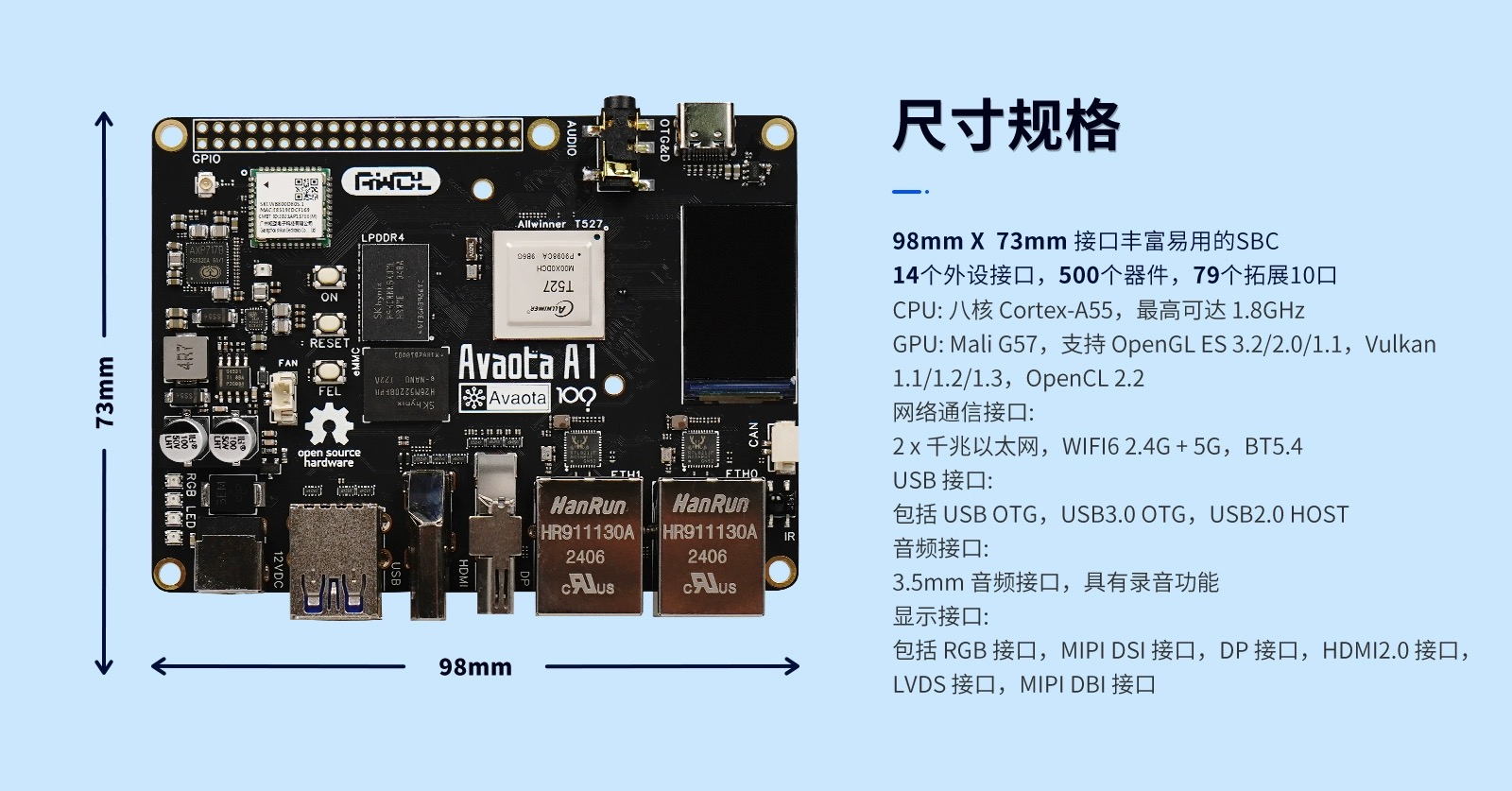

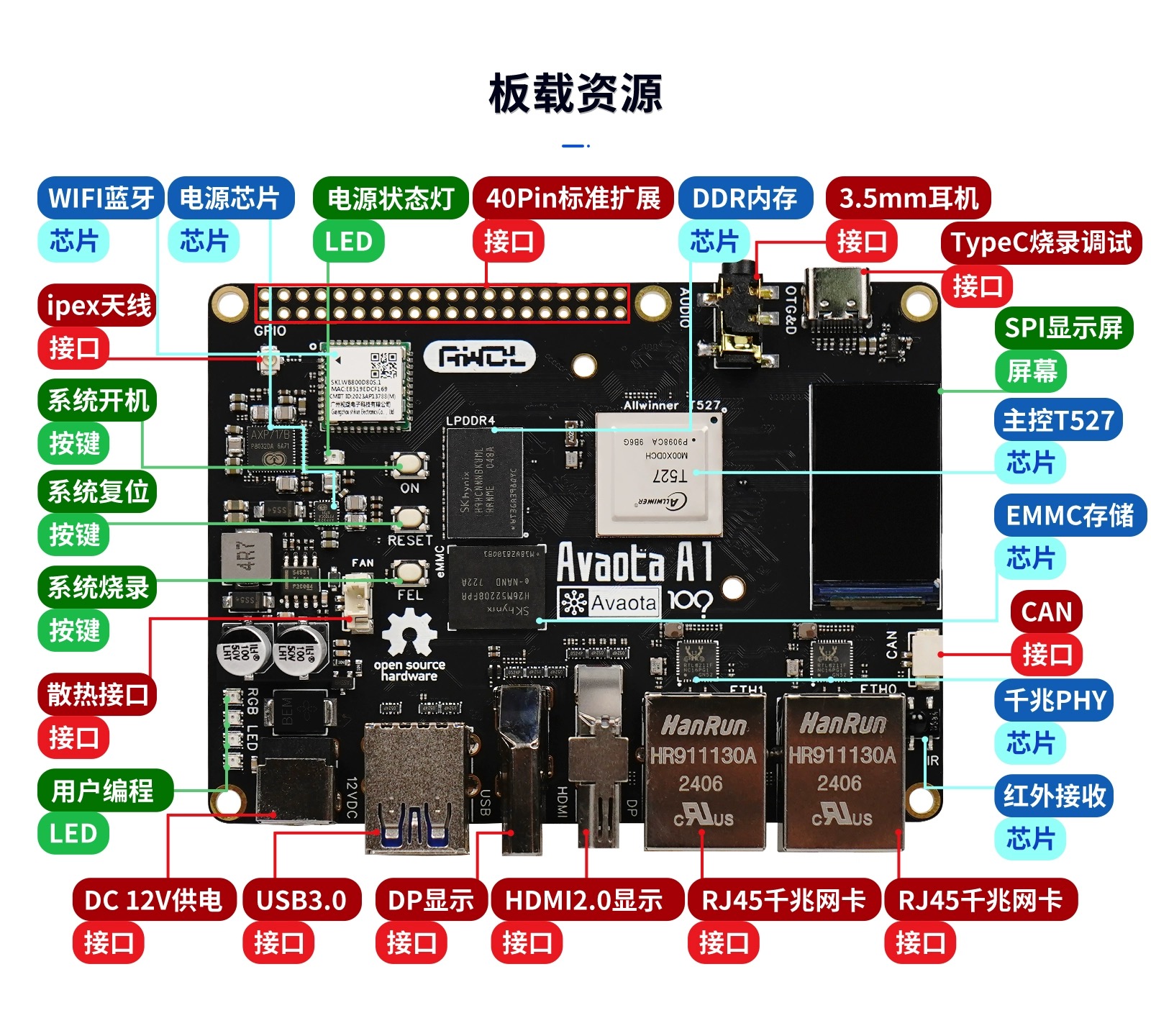

- CPU: Octa Core Cortex-A55, Highlight 2.0GHz

- GPU: Mali G57, Support for OpenGL ES 3.2/2.0/1.1,Vulkan 1.1/1.2/1.3, OpenCL 2.2

- RCPU: XuanTie E906 RISC-V @ 200MHz

- DSP: HIFI4 DSP @ 600MHz

- NPU: Optionally available for 2TOPS

- Memory chip: LPDDR 4, optional 1/2/4 GB

- Storage chip: eMMMC 5.1 support,optional 16/32/64/128GB

- Camera: MIPI CSI interface, which supports 1300 pixels, 4 circuit MIPI CSI

- Network Communication Interface: 2 x gigabytes Ethernet, WIFI6 2.4G + 5 G,BT5.4

- USB interfaces: Includes USB OTG, USSB3.0 OTG, USB2.0 HOST

- Audio interface: 3.5 mm audio interface, with audio recording

- Show interfaces: including RGB interfaces, MIPI DSI interfaces, DP interfaces, HDMI2.0 interfaces, LVDS interfaces, MIPI DBI interface

- Other Interface Modules: Including Debug Series,TF Slot,CAN Interfaces,RGB LED, Infrared (IR),UART,IIC,I2S,SPI,PWM

Detailed parameters

| Master chip T527 | CPU | Use of Occurrence Cortex-A55 |

| GPU | Mali G57 | |

| OpenGL ES 3.2/2.0/1.1 | ||

| Vulkan1.1/1.2/1.3 | ||

| OpenCL2.2 | ||

| Panforst/Mali | ||

| RCPU | XuanTie E906 RISC-V @ 200 MHz | |

| DSP | HIFI4 DSP @ 600MHz | |

| Frequency | Highest found for 1.8GHz | |

| Crafts | 22nm | |

| NPU | Up to 2TOPS | |

| Video decode | H.265/VP94K, H.264K | |

| Video encoding | H.264@60fps 1080p | |

| ISP | 8 million pixels online ISP,13 million pixels offline ISP | |

| Memory chip | LDD4 | 1/2/4GB |

| Save chip | eMMC 5.1 | 16/32/64/128GB |

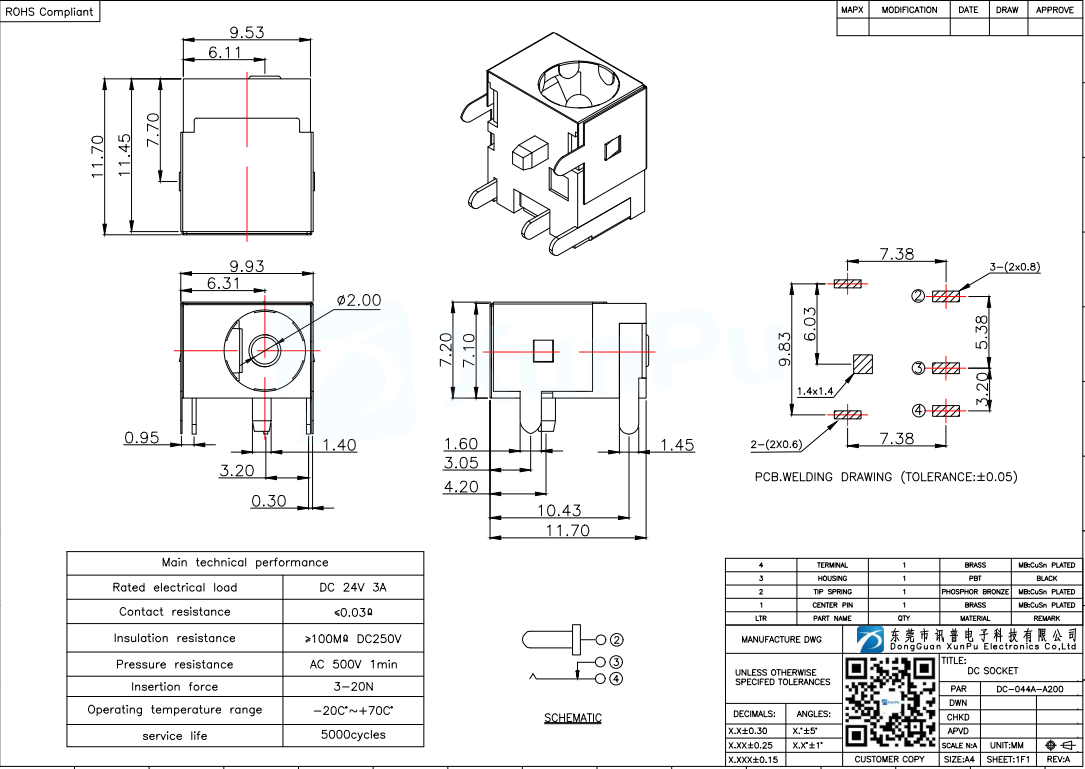

| Power | DCs Interface | 12V.2A/9V3A |

| Show interface | RGB Interface | 1080p@60fps |

| MIPI DSI interface | 2560 x 1600@60fps | |

| DP Interface | 2.5K@60fps | |

| HDMI2.0 interface | 3840 x 2160@60fps | |

| LVDS Interface | 1920x1080@60fps | |

| MIPI DBI interface | 320 x 240@60fps | |

| IIC Interface | IIC Display Screen | |

| Camera | MIPI CSI interface | 4lane MIPI CSI, 13 million pixels |

| Network Communication Interface | Wired Ethernet | 2 x gigagen Ethernet |

| WIFI Module | WIFI6 2.4G + 5G | |

| BT | BT5.4 | |

| USB interface | USB OTG | 1 x USB 2.0 OTG |

| USB3.0 OTG | 1 x USB 3.0 OTG | |

| USB HOST | 1 x USB 2.0 HOST | |

| Audio Interface | 3.5 mm Audio Interface | Very advanced, recording is supported |

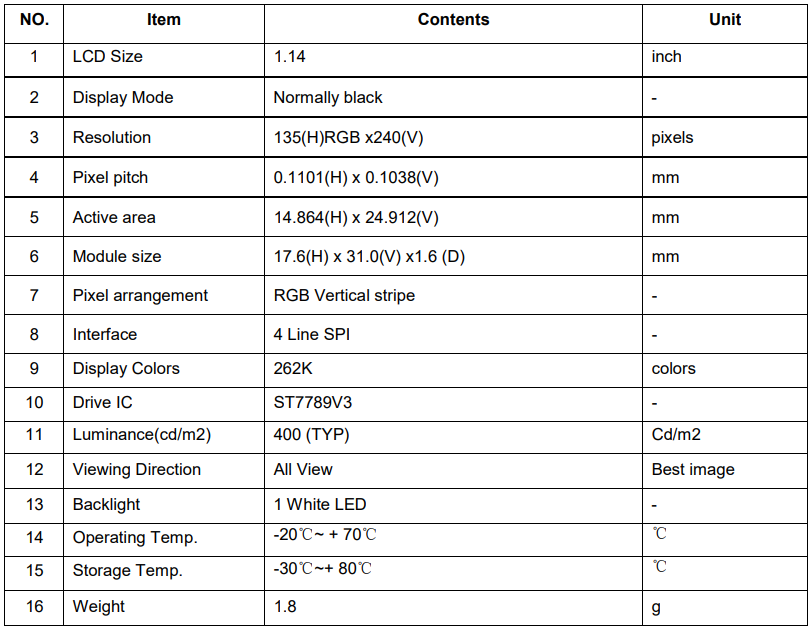

| Board Load LCD TFT | LCD Screen | 240 x 135@60fps 1.14 yun IPS screen |

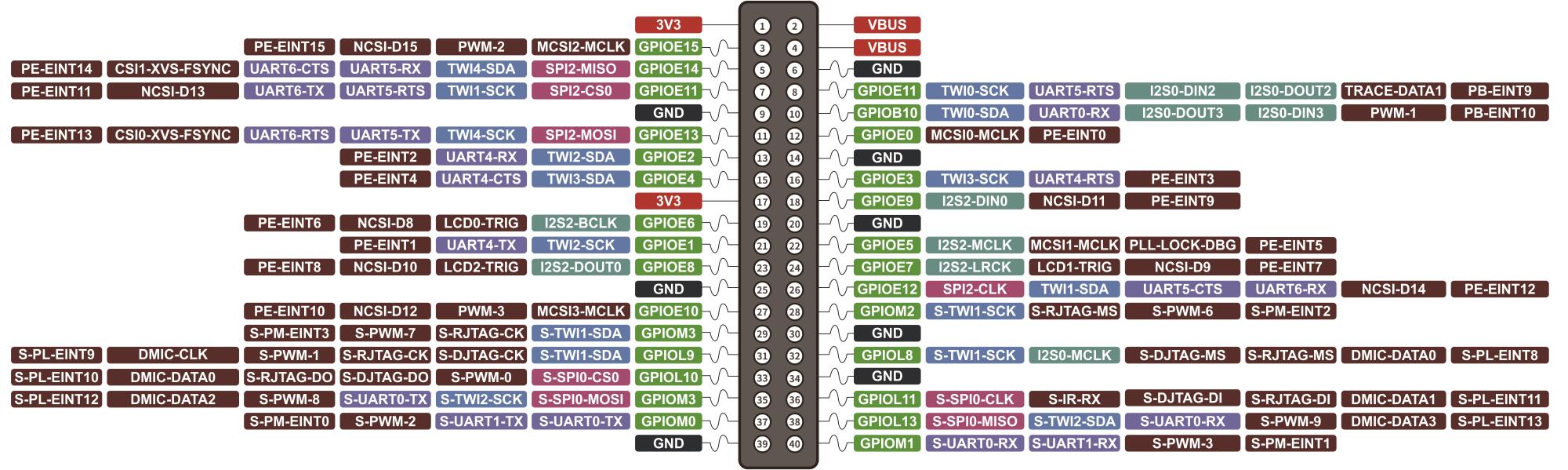

| GPIO | 40Pin GPIO | 40Pin GPIO |

| Other Interface Module | Debug Serial | Refer to 40Pin GPIO, Type-C, support |

| TF Card | SD3.0, Automatic Consultation | |

| Button | Start Key | |

| Flush Key | ||

| Reset Key | ||

| CAN | Board CAN Interface | |

| RGB LED | Board of Directors 4 at WS2812 | |

| IR | Board Infrared Receiver | |

| BIOS | Board 128M SPI NAND as BIOS | |

| Signal extension interface | UART | 4 x UART |

| IIC | 1 x IIC | |

| I2S | 1 x I2S | |

| SPI | 2 x SPI | |

| PWM | 19 x PWM |

GPIO 功能

DC 插孔规格

Tablet SPI Display Screen

Features

Design

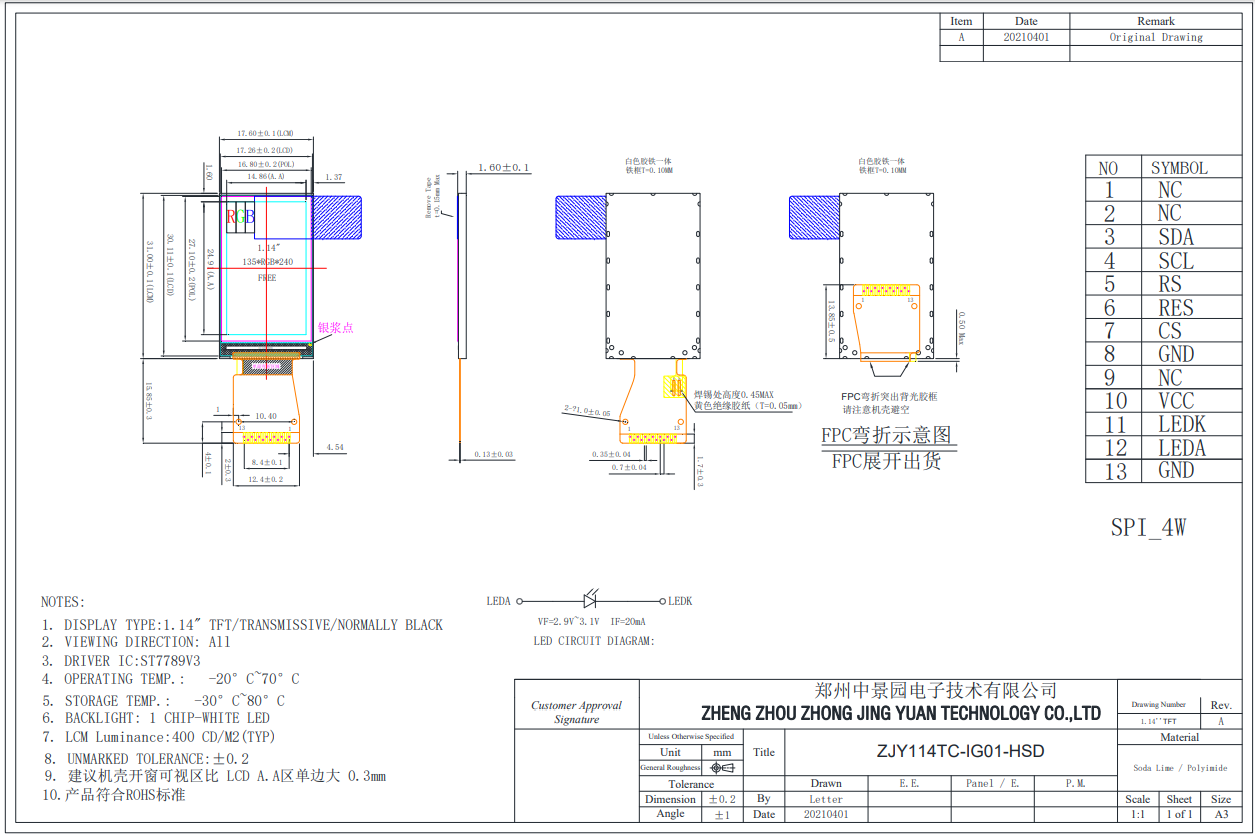

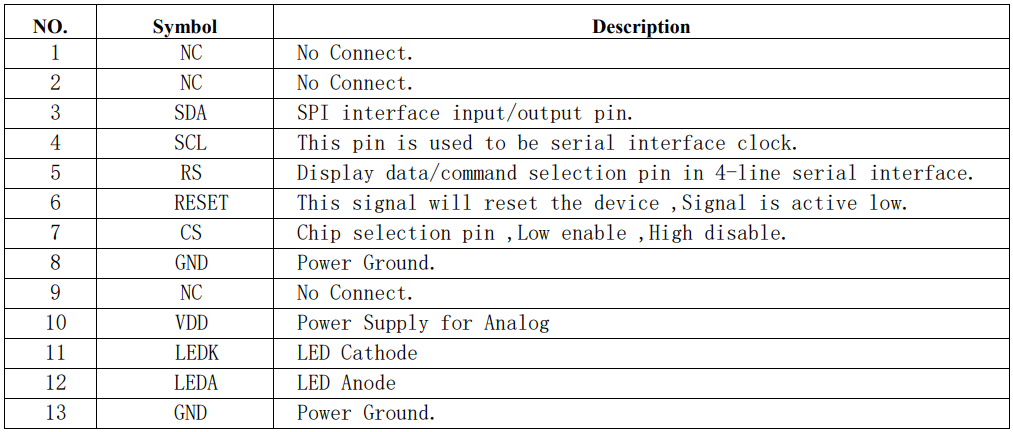

Signal definition

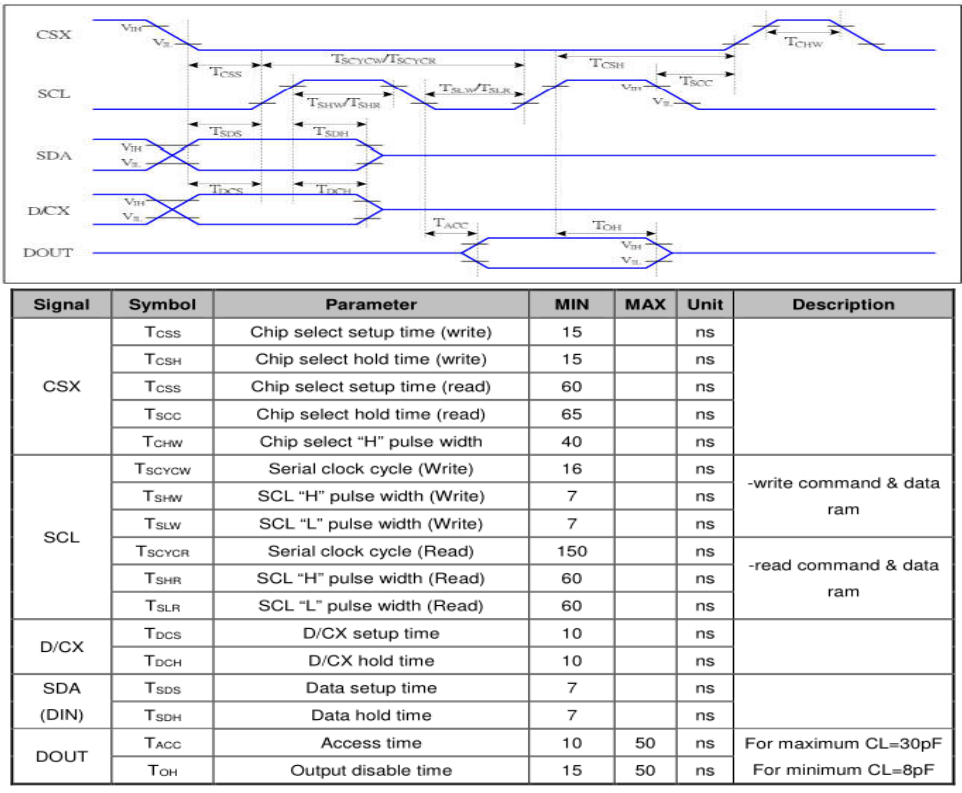

Time series parameter

Initialize Code:

LCD_Set_RES(0);

mdelay(100);

LCD_Set_RES(1);

mdelay(100);

LCD_WR_REG(0x11);

mdelay(120);

LCD_WR_REG(0x36);

LCD_WR_DATA8(0xA0);

LCD_WR_REG(0x3A);

LCD_WR_DATA8(0x05);

LCD_WR_REG(0xB2);

LCD_WR_DATA8(0x0C);

LCD_WR_DATA8(0x0C);

LCD_WR_DATA8(0x00);

LCD_WR_DATA8(0x33);

LCD_WR_DATA8(0x33);

LCD_WR_REG(0xB7);

LCD_WR_DATA8(0x35);

LCD_WR_REG(0xBB);

LCD_WR_DATA8(0x19);

LCD_WR_REG(0xC0);

LCD_WR_DATA8(0x2C);

LCD_WR_REG(0xC2);

LCD_WR_DATA8(0x01);

LCD_WR_REG(0xC3);

LCD_WR_DATA8(0x12);

LCD_WR_REG(0xC4);

LCD_WR_DATA8(0x20);

LCD_WR_REG(0xC6);

LCD_WR_DATA8(0x0F);

LCD_WR_REG(0xD0);

LCD_WR_DATA8(0xA4);

LCD_WR_DATA8(0xA1);

LCD_WR_REG(0xE0);

LCD_WR_DATA8(0xD0);

LCD_WR_DATA8(0x04);

LCD_WR_DATA8(0x0D);

LCD_WR_DATA8(0x11);

LCD_WR_DATA8(0x13);

LCD_WR_DATA8(0x2B);

LCD_WR_DATA8(0x3F);

LCD_WR_DATA8(0x54);

LCD_WR_DATA8(0x4C);

LCD_WR_DATA8(0x18);

LCD_WR_DATA8(0x0D);

LCD_WR_DATA8(0x0B);

LCD_WR_DATA8(0x1F);

LCD_WR_DATA8(0x23);

LCD_WR_REG(0xE1);

LCD_WR_DATA8(0xD0);

LCD_WR_DATA8(0x04);

LCD_WR_DATA8(0x0C);

LCD_WR_DATA8(0x11);

LCD_WR_DATA8(0x13);

LCD_WR_DATA8(0x2C);

LCD_WR_DATA8(0x3F);

LCD_WR_DATA8(0x44);

LCD_WR_DATA8(0x51);

LCD_WR_DATA8(0x2F);

LCD_WR_DATA8(0x1F);

LCD_WR_DATA8(0x1F);

LCD_WR_DATA8(0x20);

LCD_WR_DATA8(0x23);

LCD_WR_REG(0x21);

LCD_WR_REG(0x29);